# The Pennsylvania State University The Graduate School Department of Electrical Engineering

# A DIGITALLY CONTROLLED SAFETY RADAR SUBSYSTEM FOR ATMOSPHERIC LIDAR SYSTEMS

A Thesis in

Electrical Engineering

by

Scott P. Boone

Submitted in Partial Fulfillment of the Requirements for the Degree of

Master of Science

May 1995

| I grant The Pennsylvania State University the University's own purposes and to make single on a not-for-profit basis if copies are not other | e copies of the work available to the public |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|                                                                                                                                              | Scott P. Boone                               |

|                                                                                                                                              |                                              |

|                                                                                                                                              |                                              |

| We approve the thesis of Scott P. Boone.                                                       |                   |

|------------------------------------------------------------------------------------------------|-------------------|

|                                                                                                | Date of Signature |

|                                                                                                |                   |

|                                                                                                |                   |

| Charles R. Philbrick Professor of Electrical Engineering Thesis Advisor                        |                   |

|                                                                                                |                   |

| Stewart Kurtz  Murata Professor of Materials Research, and Professor of Electrical Engineering |                   |

|                                                                                                |                   |

| William Moyer<br>Research Associate                                                            |                   |

|                                                                                                |                   |

| Larry C. Burton                                                                                |                   |

| Professor of Electrical Engineering                                                            |                   |

| Head of the Department of Electrical Engineer                                                  | ering             |

#### Abstract

The operation of high power lasers in the atmosphere requires the use of safety procedures to ensure the well being of ground personnel and the safety of passengers and crew aboard aircraft operating in the local area. For an atmospheric LIDAR to be used as an autonomous instrument, safety procedures in conjunction with a safety subsystem are required. This thesis describes the design and analysis of a Safety Radar subsystem using a commercial marine radar as its primary component. The subsystem includes custom hardware to monitor the radar and disable the laser when the situation is warranted. The Safety Radar subsystem is shown to detect both private and commercial air traffic at required ranges and at speeds which allow it to inhibit laser operation well before any intercept of the laser beam can occur. Self-monitoring functions for both the radar unit and the custom hardware are demonstrated to disable the laser in the event of any detected hardware failure. A summary of key features and cautions is given along with operational considerations.

## **Table of Contents**

| List of Figu | ires                                            | vi   |

|--------------|-------------------------------------------------|------|

| List of Tab  | les v                                           | 'iii |

| Acknowled    | Igments                                         | ix   |

|              |                                                 |      |

| Chapter 1.   | Introduction                                    | . 1  |

| Chapter 2.   | Subsystem Description                           | . 5  |

| 2.1          | Commercially Available Hardware                 | . 7  |

|              | Custom Hardware - Laser Safety Radar Controller |      |

|              | Safety Radar Subsystem                          |      |

| Chapter 3.   | Subsystem Analysis                              | 12   |

|              | ~ 100,000                                       | -    |

| 3.1          | Aircraft Parameters                             | 12   |

| 3.2          | Maximum Range Analysis                          | 13   |

|              | Maximum Time to Intercept Analysis              |      |

| 3.4          | Analysis Summary                                | 25   |

| Chapter 4.   | Custom Hardware Design Description              | 27   |

| 4.1          | Ode in 1 Product                                | 27   |

|              | Original Design                                 |      |

|              | Design Overview                                 |      |

| 4.3          | Functional Description                          |      |

|              | 4.3.2 Target Detection Threshold Controller     |      |

|              | 4.3.3 Range Bin Controller                      |      |

|              | 4.3.4 Built-in-Test Functions                   |      |

|              | 4.3.5 STD Interface Controller                  |      |

|              |                                                 |      |

| Chapter 5 Safety Radar Subsystem Test                              |     |

|--------------------------------------------------------------------|-----|

| 5.1 LSRC Bench Testing                                             |     |

| 5.1.2 Target Processing Test Results                               |     |

| 5.2 Integration of the LSRC with the Raytheon Radar                |     |

| 5.2.1 Verification of Blanking and Range Bin Functions             |     |

| 5.2.2 Verification of Pulse Stagger Function                       |     |

| 5.2.3 Verification of Target Detection Threshold Function          |     |

| 5.3 SRS Testing Summary                                            |     |

| 5.5 SKS Testing Summary                                            | 31  |

|                                                                    |     |

|                                                                    |     |

| Chapter 6. Conclusions                                             | 56  |

| 6.1 Summary of Features                                            |     |

| 6.2 Operational Considerations                                     |     |

| 6.3 Suggestions for Future Work                                    |     |

|                                                                    |     |

| References                                                         | 59  |

|                                                                    |     |

|                                                                    |     |

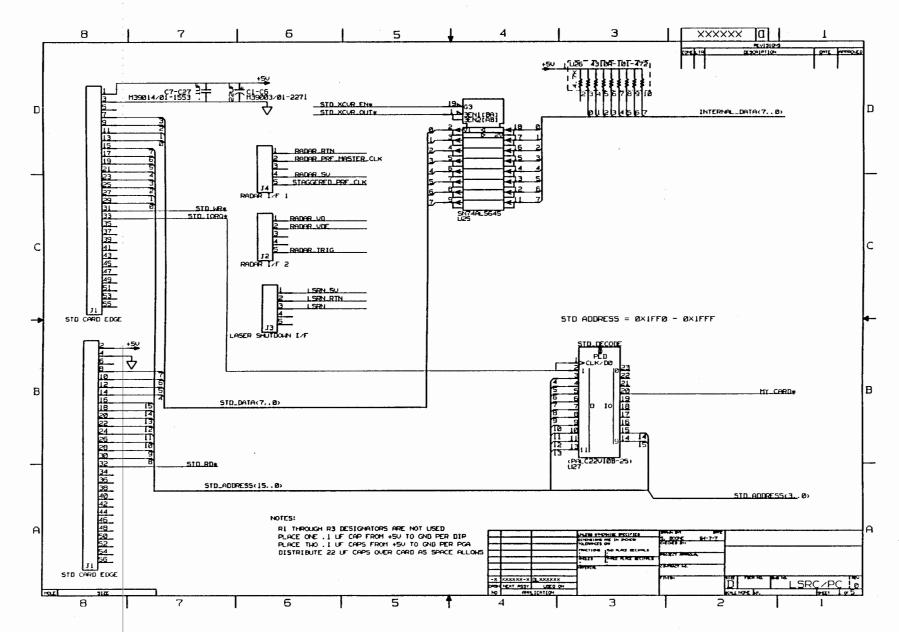

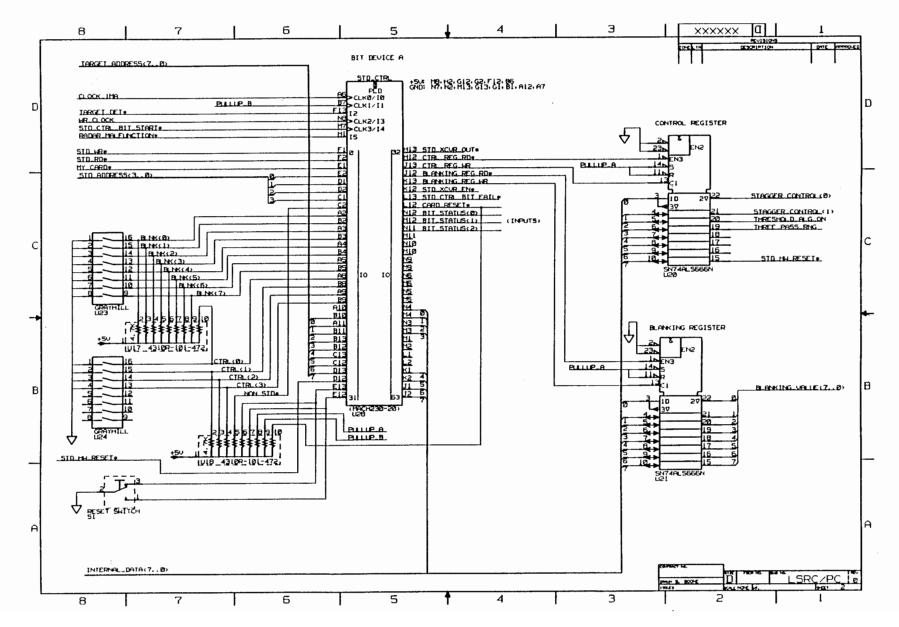

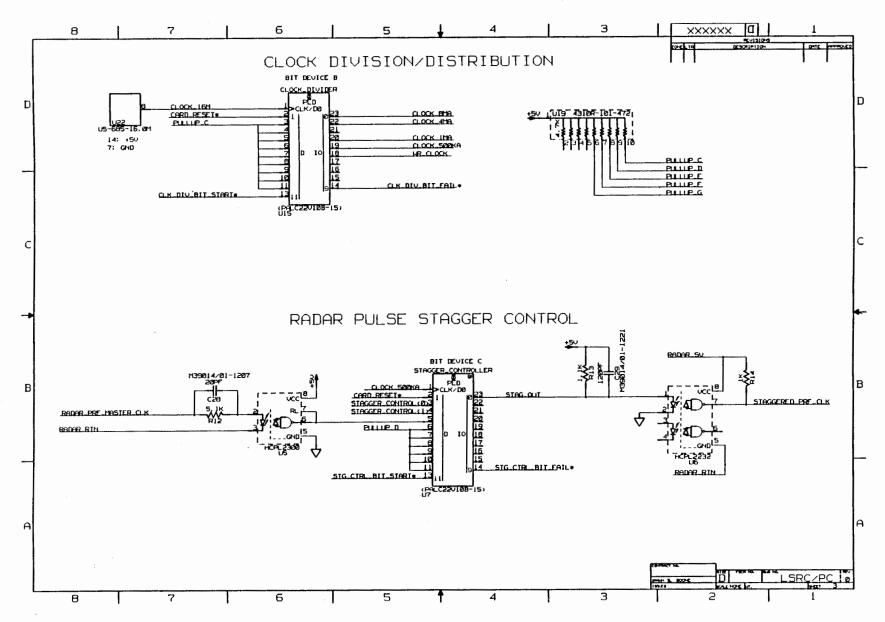

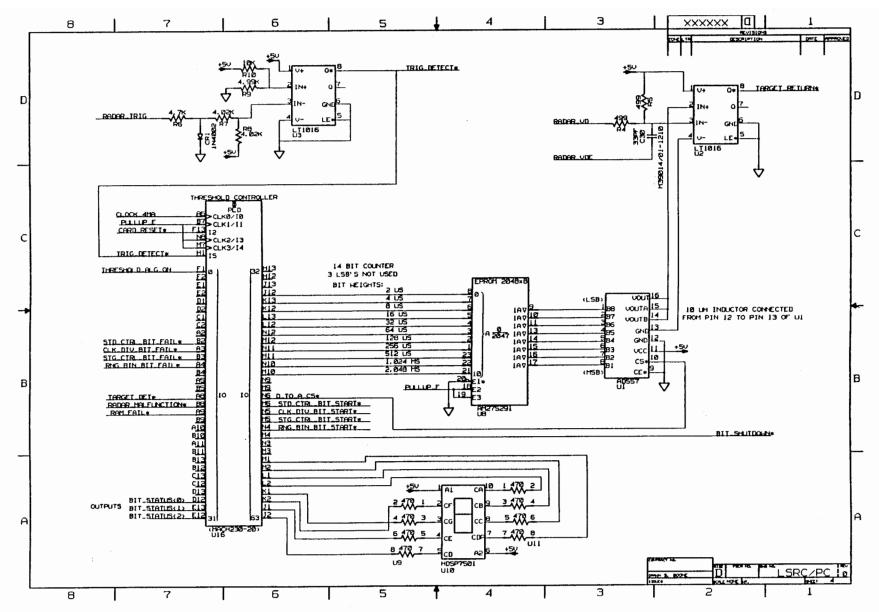

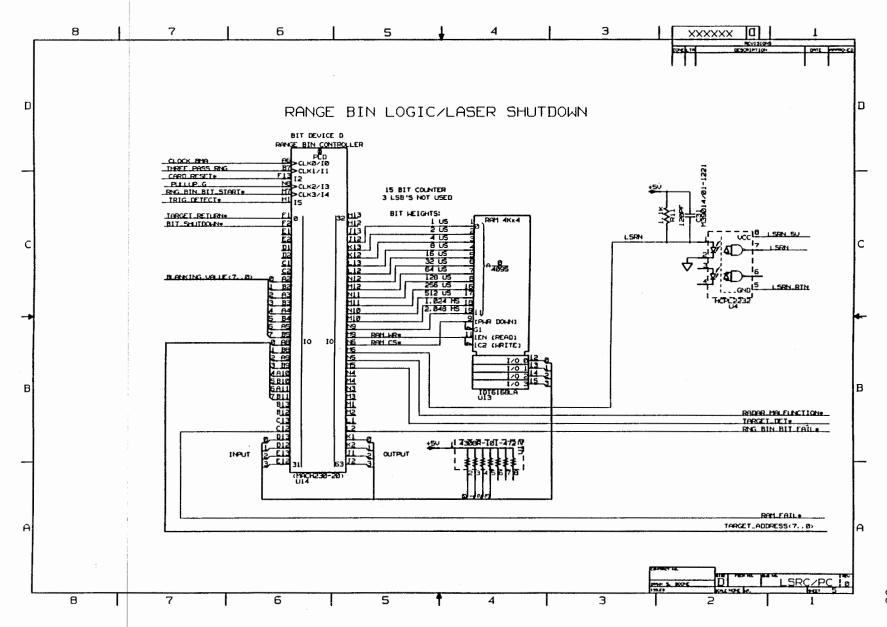

| Appendix A: LSRC Schematics                                        | 61  |

|                                                                    |     |

|                                                                    |     |

| Appendix B: LSRC Parts List                                        | 67  |

|                                                                    |     |

|                                                                    |     |

| Appendix C: LSRC Hardware-Software Interconnect Diagram            | 68  |

|                                                                    |     |

|                                                                    |     |

| Appendix D: ABEL Code for LSRC Programmable Devices                | 71  |

|                                                                    |     |

| A TOTAL OF THE THEORY IN THE PROME                                 | 100 |

| Appendix E: C Code for Generation of Threshold Control Lookup PROM | 100 |

|                                                                    |     |

| Annualis E. MATI AD Code for Thesis Colonistics                    | 105 |

| Appendix F: MATLAB Code for Thesis Calculations                    | 105 |

# List of Figures

| 2.1 | Safety Radar subsystem parameter definition                        |

|-----|--------------------------------------------------------------------|

| 2.2 | Seavey Engineering antenna, gain (dB) versus angle (degrees)       |

| 2.3 | Safety Radar subsystem block diagram                               |

| 3.1 | Maximum range versus radar cross section                           |

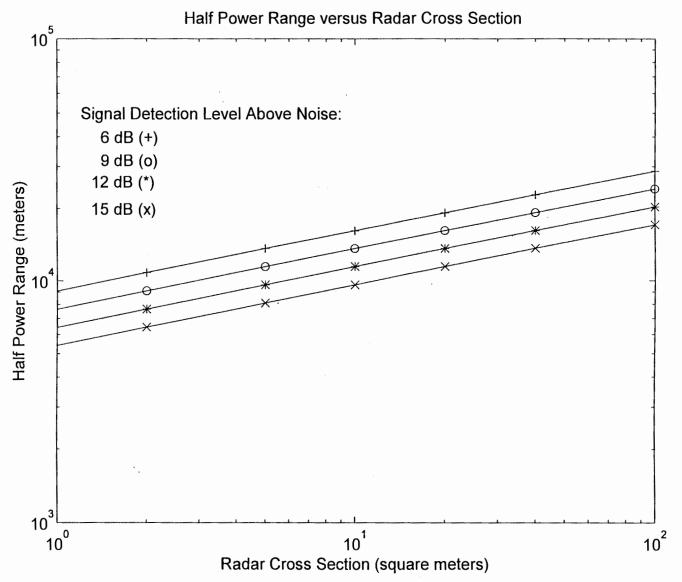

| 3.2 | Half power range versus radar cross section                        |

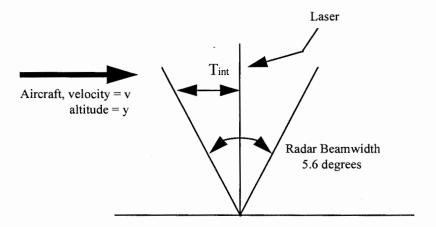

| 3.3 | Calculation for time from detection to intercept, T <sub>int</sub> |

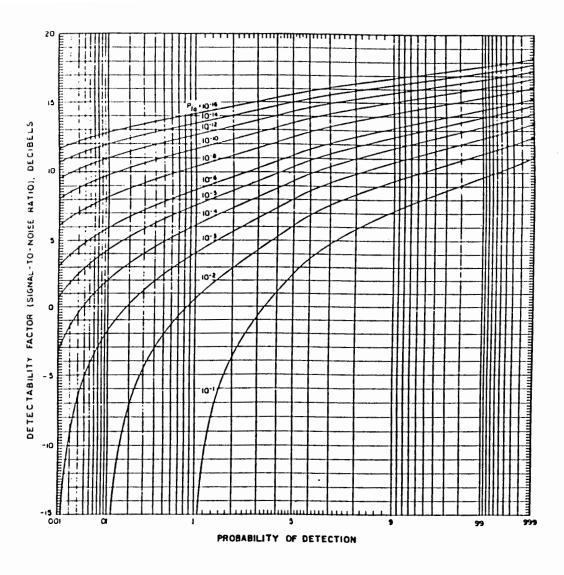

| 3.4 | Required signal-to-noise ratio for single pulse detection          |

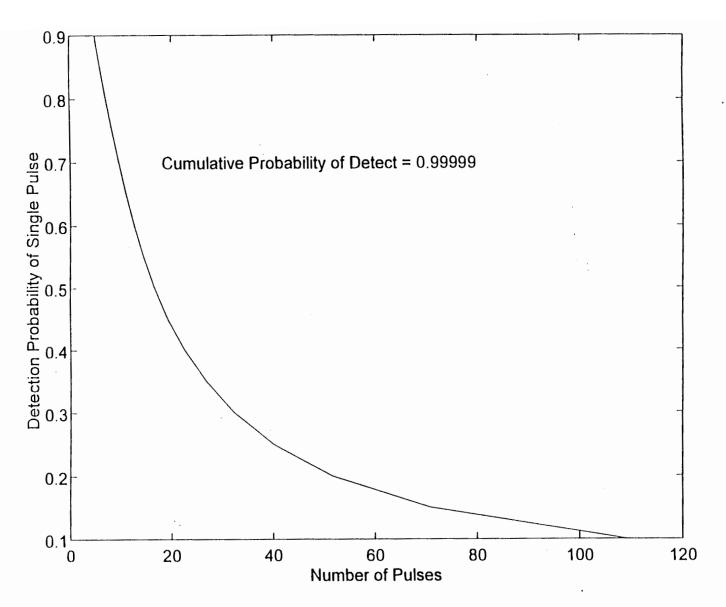

| 3.5 | Probability of detection for single radar pulse                    |

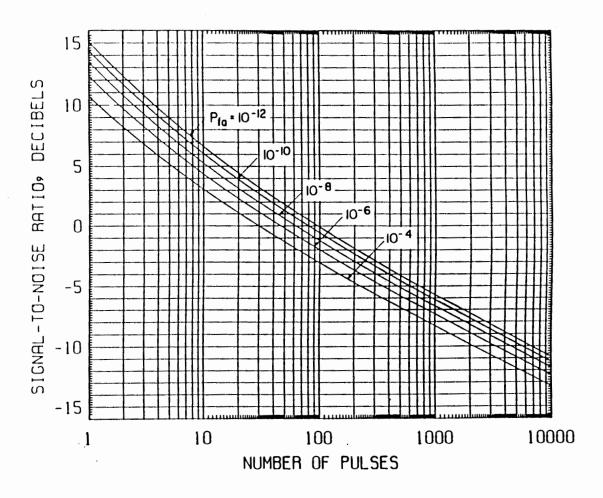

| 3.6 | Required signal-to-noise ratio for detection of n pulses           |

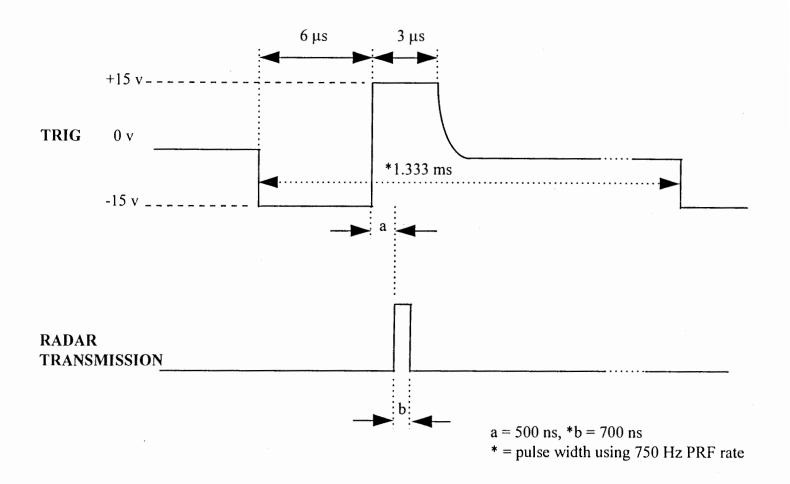

| 4.1 | Relationship of radar TRIG signal to actual radar transmission     |

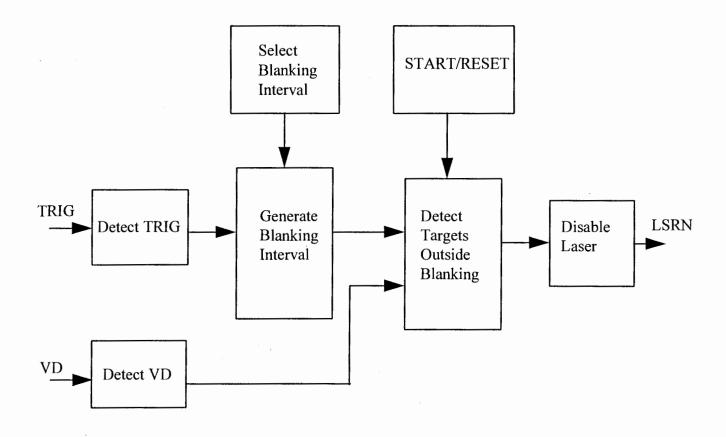

| 4.2 | Block diagram of original laser safety controller circuit          |

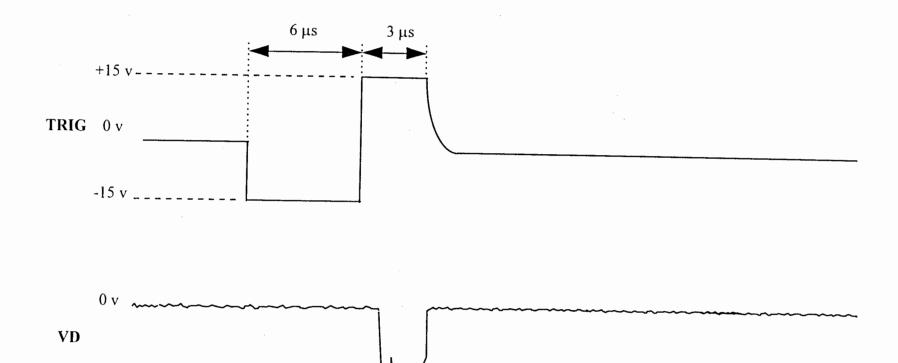

| 4.3 | Relationship of radar VD signal to radar TRIG signal               |

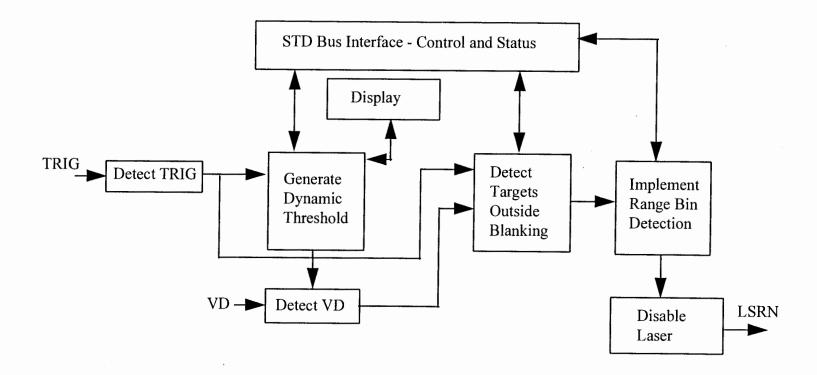

| 4.4 | LSRC block diagram - main processing                               |

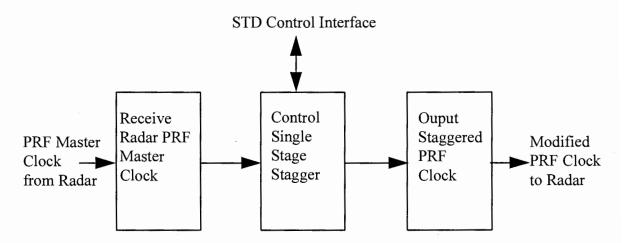

| 4.5 | LSRC stagger controller block diagram                              |

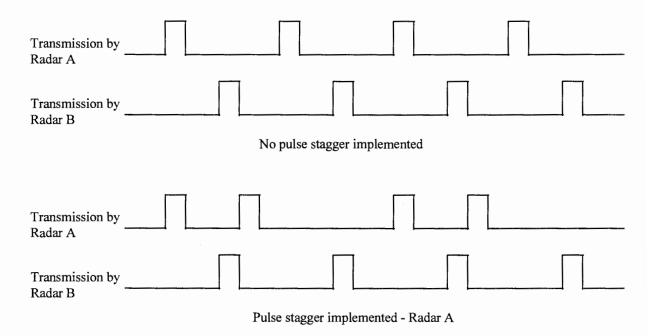

| 4.6 | Pulse staggering of a radar transmission                           |

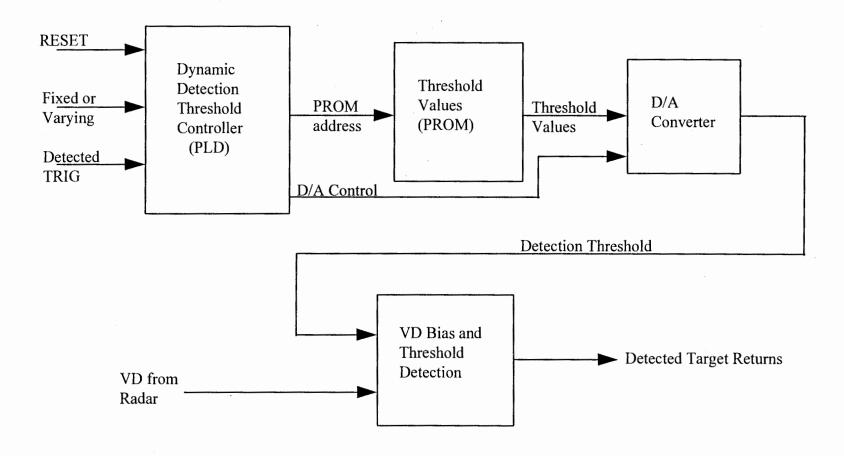

| 4.7 | Target detection threshold controller block diagram                |

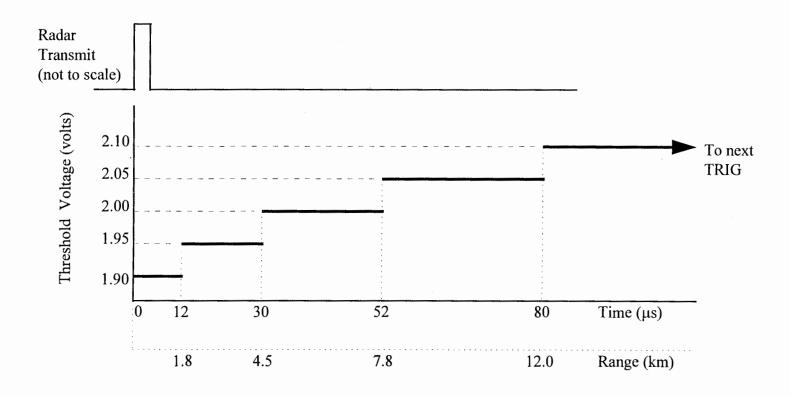

| 4.8 | Detection threshold values relative to radar pulse transmission    |

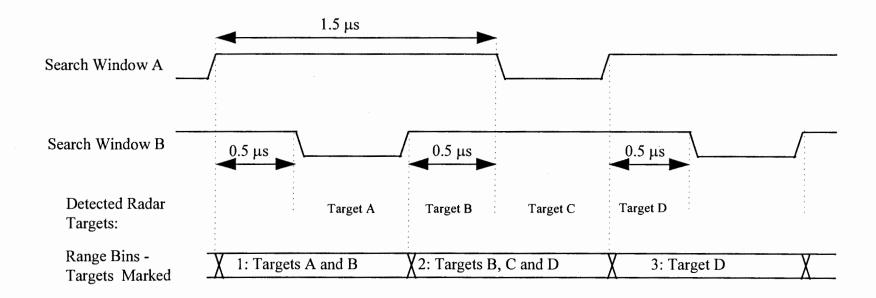

| 4.9 | LSRC target search and range bin algorithm                         |

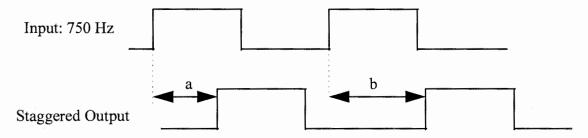

| 5.1 | Measured delay of staggered output                                 |

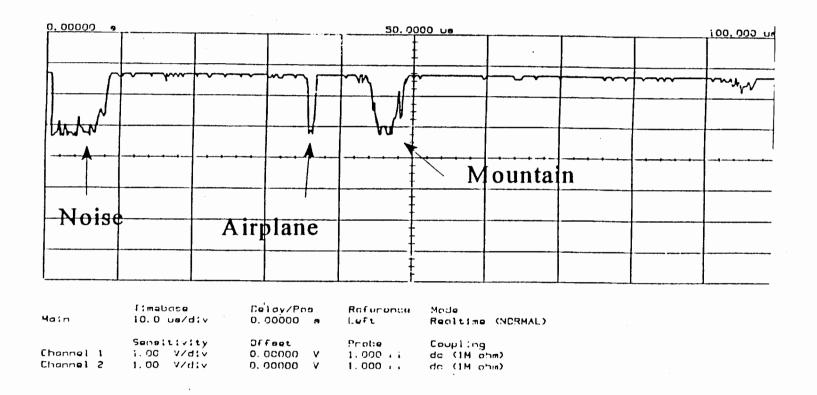

| 5.2 | Time plot of R72 radar detection of aircraft at 5.3 km range       |

## List of Tables

| 2.1 | Raytheon R72 radar specifications                     | 7  |

|-----|-------------------------------------------------------|----|

| 2.2 | Parabolic antenna specifications                      | 8  |

| 3.1 | Representative aircraft speeds and altitudes          | 12 |

| 3.2 | Representative aircraft radar cross sections          | 13 |

| 3.3 | Summary for maximum range calculation                 | 15 |

| 3.4 | Summary for half power range calculation              | 15 |

| 3.5 | Scattering loss of 9.4 GHz signal transmitted in rain | 26 |

| 4.1 | LSRC encoded display interpretation                   | 45 |

| 5.1 | Measured delay values of staggered output             | 48 |

| 5.2 | LSRC response to simulated radar targets              | 49 |

#### Acknowledgments

I would like to express appreciation to my thesis advisor, Dr. C. R. Philbrick, for his encouragement and advice during the past year. I would like to thank Dr. Stewart Kurtz and Bill Moyer for serving on my thesis committee.

Many others have helped me through this long process, some offering technical assistance and others, wise counsel. Many of you just sat quietly while I "discussed" the technical issues written on these pages. This type of support is invaluable. To Mark Bregar, Dr. William Blum, Wayne Solbrig, Jack Woika, Jim Ross, Jeff Weber, and Jonathan Eckert, I offer a heartfelt thank you. The technical assistance of Tom Petach, David Blood, Dr. Daniel Lysak, Glenn Pancoast, Jeff A. Hamilton and Scott Kriner was also greatly appreciated.

A word of appreciation to my wonderful family, my wife, Lesa, my son, Tyler and baby-to-be, for their ongoing love and support and to my parents for their love and for making my education possible.

#### Chapter 1

#### Introduction

This thesis presents a detailed study of the development of the Safety Radar subsystem for use as a safety mechanism for atmospheric LIDAR (Light Detection and Ranging) systems. It shows the subsystem in a top-down fashion, starting with a subsystem definition followed by a parameter definition and analysis. It continues with a description of the functional design of basic hardware components, a discussion of subsystem testing, and concludes with a subsystem specification.

LIDAR systems direct a high power laser beam into the sky to measure profiles of atmospheric properties. The laser pulses, on the order of tens of nanoseconds duration, must be of high enough energy to produce measurable back-scattering from molecules and particles. Typical LIDAR applications use laser beams with 0.5 to 2 joules per pulse. These several hundred megawatt pulses are a hazard to the human eye for intraocular vision of the beam. Light passing through the lens of the eye is focused directly onto the highly sensitive retina. Only a small amount of optical energy directed at the eye will cause permanent retinal damage [1]. Experimental data shows that for a pulsed laser transmitting at 500 to 700 nm, retinal damage can occur at levels as low as  $70 \times 10^{-6}$  J/cm<sup>2</sup> [2]. Because of the optical hazard inherent in the high intensity laser pulse, strict safety procedures must be observed by operators of atmospheric LIDAR systems to avoid any direct intraocular vision of the beam.

With no precautions in place, aircraft could be illuminated by the laser causing unpredictable specular reflections from portions of the craft's surface. The reflection hazard,

along with the remote possibility of an aircraft passenger or pilot looking directly into the laser beam must be avoided. Safety procedures which inhibit the operation of the LIDAR system during periods when aircraft are near the laser provide one mechanism to ensure eye safety for aircraft crew and passengers, and ground based personnel.

The use of a human observer with a laser override switch is one solution to the safety problem. For short term operation of the laser, stationing one or two persons to observe aircraft activity provides the required safe operating environment, particularly in areas with modest air traffic. Observers are tasked with monitoring local air traffic and activating the laser override when an aircraft's flight path brings it into a predetermined area. The present operation of lasers in the vicinity of State College, Pennsylvania relies upon the use of safety observers. This operating procedure has been approved by the Federal Aviation Administration (FAA) for a site at the west end of the Pennsylvania State University campus. Similar operating procedures have been approved and used in many locations where laser beams are propagated in the atmosphere.

An automatic LIDAR system, one which would operate with minimal human interaction, has many potential applications. Such a system could monitor weather conditions in remote areas and transmit data to centralized sites. In many cases, this system could eventually replace the need for the launch of meteorological rockets and balloons [3]. In order to move the design of atmospheric LIDAR systems toward a goal of becoming an autonomous instrument, a reliable automatic safety subsystem must be developed. A radar based subsystem provides the search and detection capability required for this application.

Radar systems are used in many safety applications including air traffic control in busy flight corridors and ground-based collision avoidance systems. The role of a radar subsystem for an atmospheric LIDAR application is also one of safety. Instead of warning aircraft or ground based personnel of a potential hazard, the main requirement of this subsystem is to disable the operation of the laser beam well in advance of any aircraft intercept. Radar systems have been used in previous LIDAR instruments for the same purposes as those described here [4].

Chapter 2 defines the Safety Radar subsystem at a top level and shows the necessary parameters to describe it. Subsystem components are defined along with a discussion of how they relate to defined parameters. Tradeoffs for the high level components are discussed. Chapter 3 summarizes the top level requirements and describes how these requirements are satisfied by the subsystem. This section contains a detailed analysis of the subsystem's performance. Chapter 4 contains a detailed analysis of the custom hardware developed for the subsystem by the author and shows how it satisfies the requirements allocated to it. A discussion of the first generation of the hardware is included to further show the subsystem's present functionality. Chapter 5 includes discussions of proof-of-design and proof-of-performance tests that were performed on the subsystem and its components along with pertinent data taken during this testing. Chapter 6 concludes the thesis with a discussion of the subsystem's key features and a caution concerning the potential implementations of the subsystem. Operational considerations are discussed to summarize the uses of the

subsystem. An appendix is included containing hardware documentation, programming information for the subsystem, and MATLAB code used for analysis and calculations.

#### Chapter 2

#### **Subsystem Description**

A radar subsystem to guard against potential intercepts of a laser beam must fulfill two basic requirements. Because lasers used in the current LIDAR systems have an eye safe distance of 180 km for intraocular vision [3], the radar subsystem must have sufficient range to detect aircraft up to their maximum operating altitudes or maximum range from the radar. It must also determine a potential intercept of the laser beam with sufficient speed and reliability to guarantee the laser is disabled and remains in that state until the hazard no longer exists. These requirements are discussed in general in this chapter to show the development of the overall subsystem.

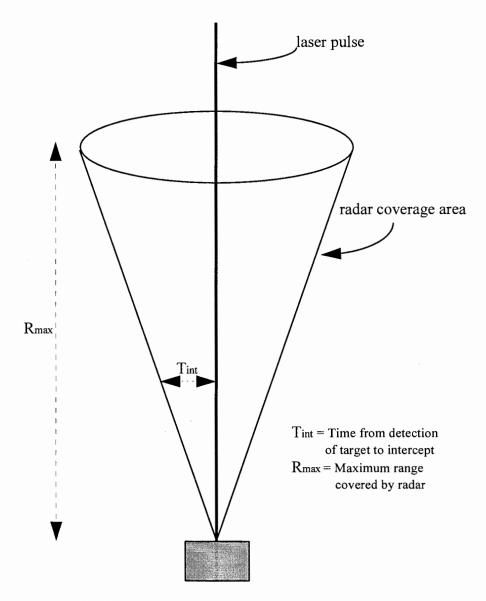

Figure 2.1 illustrates the primary parameters that define the Safety Radar subsystem;  $R_{\text{max}}$  and  $T_{\text{int}}$ .  $R_{\text{max}}$  is defined as the maximum range at which an aircraft is detectable by the subsystem.  $T_{\text{int}}$  is defined as the time from the first detection of an aircraft to the time it would intercept the laser. The subsystem must respond to a detection before this maximal parameter is reached. The Safety Radar subsystem's performance will be shown to meet necessary values for these parameters in the next chapter.

Commercially available radar systems offer the capability necessary to detect commercial and private aircraft at all possible altitudes and velocities. Several types of commercially available systems were evaluated including aircraft collision avoidance systems and marine radar systems. The latter provides the most cost effective solution while still maintaining needed performance. Because marine radar systems are in wide general use, they are easily maintained and repaired with readily available parts. The use of a marine

radar also produces some level of insensitivity to environmental changes. The radar set chosen for this application is a Raytheon R70 Series Marine Radar system.

Atmospheric LIDAR with Safety Radar Subsystem

Figure 2.1 Safety Radar subsystem parameter definition.

#### 2.1 Commercially Available Hardware

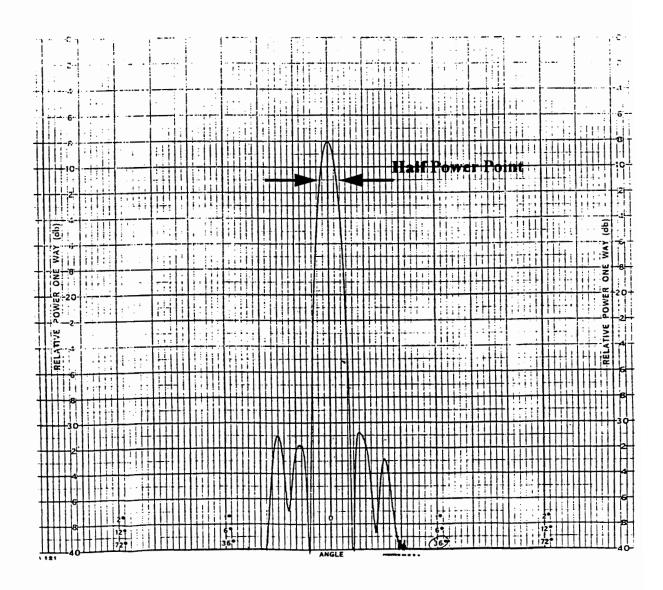

The Raytheon Model R72 Raster Scan radar system is one example of a commercially available radar unit. It is a popular commercial and civilian marine radar. Its specifications are listed in Table 2.1 [5]. While the R72 provides adequate radar performance for this application, and is the major element in the subsystem, it alone does not provide the total solution. The sweep antenna common to this and most other marine radar systems does not lend itself to use in monitoring the area necessary to protect the airspace surrounding a laser beam. A parabolic antenna yields the desired conical area of coverage for the radar subsystem. Specifications for one such antenna are listed in Table 2.2 [6]. This antenna, model number AS15-90, is available from Seavey Engineering Associates. Its gain characteristic versus angle is shown in Figure 2.2.

Table 2.1 Raytheon R72 radar specifications [5].

| Specification                                   | Value                                                                        |

|-------------------------------------------------|------------------------------------------------------------------------------|

| Transmitting Frequency                          | 9410 +/- 30 MHz                                                              |

| Transmitting Power (peak)                       | 10,000 W                                                                     |

| Pulse Length @ Pulse Repetition Frequency (PRF) | 0.08 μs @ 2000 Hz<br>0.25 μs @ 1500 Hz<br>0.7 μs @ 750 Hz<br>0.7 μs @ 500 Hz |

| Radar Receiver:                                 |                                                                              |

| Intermediate Frequency (IF)                     | 60 MHz                                                                       |

| Bandwidth                                       | 15 MHz @ 0.08 μs PRF<br>3 MHz @ all other PRF rates                          |

| Noise Figure                                    | < 6 dB maximum                                                               |

Table 2.2 Parabolic antenna specifications [6].

| Specification           | Value       |  |

|-------------------------|-------------|--|

| Beam Width (half-power) | 5.6 degrees |  |

| Efficiency@9400 MHz     | 60 percent  |  |

| Gain (G)                | 30 dB       |  |

The Raytheon radar system with the modification of a parabolic antenna does not provide a complete solution for the design of the Safety Radar subsystem. The radar system is designed primarily to identify potential hazards for sea going vehicles. It includes a manmachine interface - a keypad for parameter entry and a video monitor to display potential targets in the radar's range. A direct link between the subsystem and the LIDAR system's laser firing circuit is necessary to control automatic shutdown of the laser anytime a potential intercept of the beam by an aircraft is detected. Custom designed hardware is used to interface the radar to the laser.

#### 2.2 Custom Hardware - Laser Safety Radar Controller

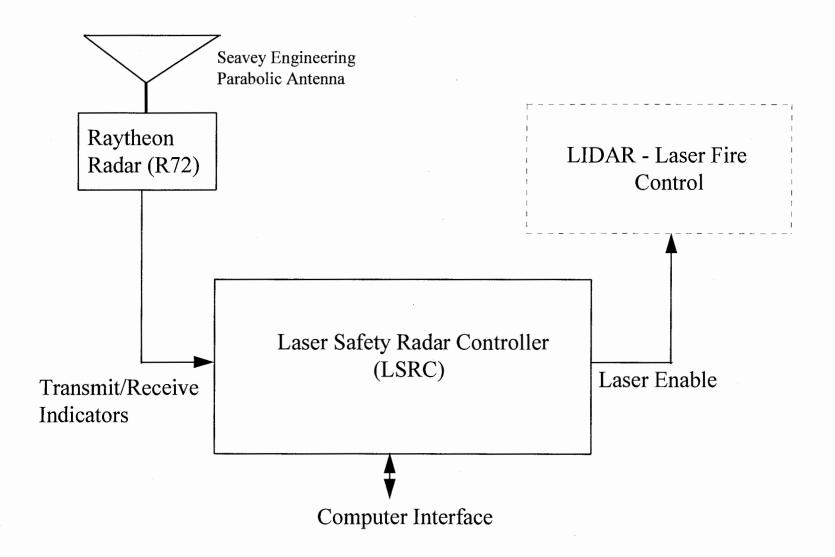

Figure 2.3 illustrates a top level block diagram for the entire safety radar subsystem.

The Laser Safety Radar Controller (LSRC) shown in the block diagram is the custom interface between the Raytheon R72 radar and the fire control for the LIDAR's laser.

Chapter 4 is devoted to an explanation of the LSRC's background and detailed design.

Indicators for the transmitted radar pulses and target returns are passed from the radar to the LSRC where they are examined and decisions are made about potential targets.

Figure 2.2 Seavey Engineering antenna, gain (dB) versus angle (degrees) [6].

Figure 2.3 Safety Radar subsystem block diagram.

The LSRC supplies an enable signal to the LIDAR's laser control circuit. This enable must be present for the laser to be fired. Once identification of a potential target has been made or in the event of a hardware failure, the laser is disabled. A computer interface to the LSRC allows for operation of the entire subsystem using embedded control code. The LSRC performs self monitoring of several of its functions as well as functions of the R72. In the event of a detected failure of the LSRC or the R72 radar, the LIDAR's laser is disabled.

#### 2.3 Safety Radar Subsystem

The Raytheon R72 radar, without the display interface or the delivered sweep antenna, are combined with the parabolic antenna and the LSRC defined above to make up the Safety Radar subsystem. The maximum detectable range parameter is directly related to the radar's transmitted power, receiver sensitivity and antenna gain specifications. It will be shown that the Safety Radar subsystem is capable of meeting or exceeding a value for R<sub>max</sub> that safely covers commercial air traffic. The time to intercept parameter, T<sub>int</sub> is related to both the radar's pulse repetition frequency (PRF) and the electronic response time of the LSRC. This parameter can also be viewed as a specification on the maximum velocity of an aircraft at a given altitude. The Safety Radar subsystem will be shown to have a probability of detection of commercial aircraft targets that approaches one. The analysis of these parameters is shown in Chapter 3.

#### Chapter 3

#### **Subsystem Analysis**

#### 3.1 Aircraft Parameters

In order to analyze the performance of the Safety Radar subsystem, it is first necessary to discuss the parameters that describe the aircraft that it will detect. Table 3.1 lists the maximum speed and maximum certified service ceiling for three classes of aircraft [7]. The classes were chosen to provide a set of speeds and altitudes which are representative of the extremes encountered by the radar.

Table 3.1 Representative aircraft speeds and altitudes [7].

| Aircraft Class                         | Maximum Level Speed<br>km/hr (miles/hour) | Service Ceiling<br>km (kft) |

|----------------------------------------|-------------------------------------------|-----------------------------|

| Small Private (Piper Cub)              | 210 (130)                                 | 5.8 (19)                    |

| Midsize Commercial<br>(Boeing 737-200) | 856 (530)                                 | 10.7 (35)                   |

| Large Commercial (Boeing 747-400)      | 981 (608)                                 | 13.7 (45)                   |

An estimate of the radar cross section for each representative aircraft is also needed to prove subsystem performance. The radar cross section of a given radar target can vary widely based on the angle of incidence and transmitting frequency of the radar. The aspects which provides the minimum possible radar cross section to a radar are a nose view and a tail view. A top, bottom or broadside view represent the maximum radar cross section for a radar target. The Safety Radar subsystem is intended for use as a vertically pointing system with a half power beamwidth of 5.6 degrees. Commercial aircraft encountered by the radar therefore will be in relatively shallow dive or climb angles or in level flight relative to the

radar beam. Estimates of typical radar cross sections for the representative classes are given in Table 3.2 [8,9].

Table 3.2 Representative aircraft radar cross section estimates [8,9].

| Aircraft Class     | Radar Cross Section (square meters) |

|--------------------|-------------------------------------|

| Small Private      | 1- 20                               |

| Midsize Commercial | 20 - 40                             |

| Large Commercial   | 40 -100                             |

These estimates shown in Table 3.2 represent minimum radar cross section values excluding nose and tail views. For the Safety Radar subsystem to encounter nose and tail aspects, aircraft would be required to dive or climb at extreme angles relative to the radar detection zone.

#### 3.2 Maximum Range Analysis

The analysis of the maximum range for the Safety Radar subsystem is based on a minimum detectable signal level. A rule of thumb for RF receiver design is that a signal is regarded as detectable if it is at least 6 dB above the receiver noise floor. The thermal noise voltage in a receiver can be described statistically as a complex Gaussian process having a zero mean and a variance of half of the noise power [10]. A signal which is 6 dB higher than the noise or on the order of four times the power of the noise is considered to be detectable. To perform the maximum range analysis, the noise floor of the radar receiver is defined as

$$R_{\text{noise}} = kT + 10 \log(BW) + NF, \tag{3.1}$$

where:

kT = noise in a 50 ohm resistor at room temperature = -174 dBm/Hz,

BW = radar receiver bandwidth = 3 MHz,

NF = radar receiver noise figure = 6 dB [5].

For the Safety Radar subsystem's radar,  $R_{noise} = -103.23$  dBm. Values for the minimum detectable signal above this noise floor,  $S_{min}$ , are then considered in the calculation for the maximum range of the subsystem. This range is given by [8]

$$R_{\text{max}} = \sqrt[4]{\frac{PWR * G^2 * \lambda^2 * \sigma}{(4\pi)^3 * S_{\text{min}}}},$$

(3.2)

where:

PWR = radar transmitting power = 10000 W,

G = antenna gain = 30 dB,

$\lambda$ = transmitter wavelength = 0.032 meters,

$\sigma$  = radar cross section of the target in square meters.

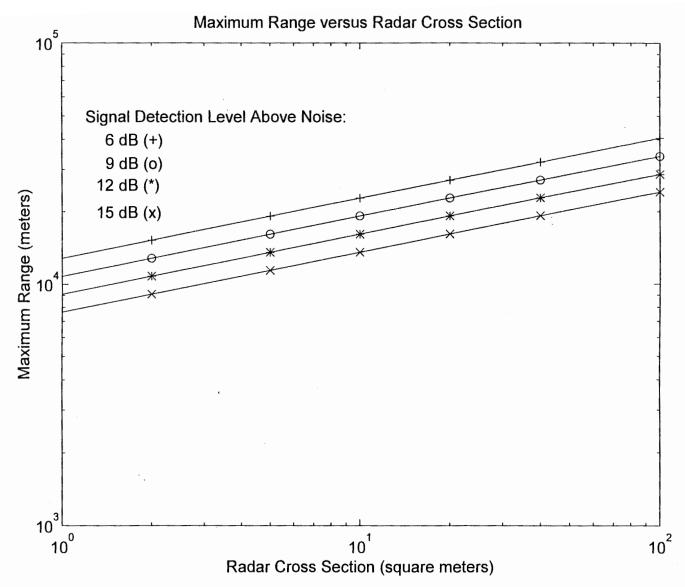

Figure 3.1 and Table 3.3 show the results for the maximum range calculation of the Safety Radar subsystem versus the radar cross section of a target aircraft. The values for  $S_{min}$  considered are 6 dB, 9 dB, 12 dB and 15 dB. The MATLAB program used to generate the data is included in Appendix F. This calculation illustrates the maximum detection capability of the subsystem by using the full gain value of the antenna. An aircraft is shown to be detectable by the radar at altitudes much higher than those achievable by the representative aircraft for minimum detectable signals from 6 dB to 15 dB above the receiver noise floor.

Next it is necessary to show the detection ranges available to the radar at the halfpower point of the antenna or 2.8 degrees off of the vertical axis. This will show the detectable altitudes for aircraft at the outer edge of the detection zone. Note that while the minimum detectable signal values considered in this calculation remain the same, the gain value is 3 dB lower at the half power point of the antenna than at its main lobe. The results of this calculation are shown in Figure 3.2 and Table 3.4.

Table 3.3 Summary of maximum range calculation.

| Radar Cross Section | Max Range in km (kft): |                  |                   |                   |  |  |

|---------------------|------------------------|------------------|-------------------|-------------------|--|--|

| (square meters)     |                        |                  |                   |                   |  |  |

|                     | $S_{min} = 6 dB$       | $S_{min} = 9 dB$ | $S_{min} = 12 dB$ | $S_{min} = 15 dB$ |  |  |

| 1                   | 12.8 (42)              | 10.8 (35)        | 9.1 (30)          | 7.6 (25)          |  |  |

| 5                   | 19.2 (63)              | 16.1 (53)        | 13.6 (45)         | 11.4 (37)         |  |  |

| 10                  | 22.8 (75)              | 19.2 (63)        | 16.1 (53)         | 13.6 (45)         |  |  |

| 20                  | 27.1 (89)              | 22.8 (75)        | 19.2 (63)         | 16.1 (53)         |  |  |

| 40                  | 32.2 (106)             | 27.1 (89)        | 22.8 (75)         | 19.2 (63)         |  |  |

| 100                 | 40.6 (130)             | 34.1 (112)       | 28.7 (95)         | 24.2 (79)         |  |  |

Table 3.4 Summary of half power range calculation.

| Radar Cross Section (square meters) | 3 dB Range in km (kft): |                  |                   |                   |  |  |

|-------------------------------------|-------------------------|------------------|-------------------|-------------------|--|--|

|                                     | $S_{min} = 6 dB$        | $S_{min} = 9 dB$ | $S_{min} = 12 dB$ | $S_{min} = 15 dB$ |  |  |

| 1                                   | 9.1 (30)                | 7.6 (25)         | 6.4 (21)          | 5.4 (17)          |  |  |

| 5                                   | 13.6 (45)               | 11.4 (37)        | 9.6 (32)          | 8.1 (27)          |  |  |

| 10                                  | 16.1 (53)               | 13.6 (45)        | 11.4 (38)         | 9.6 (32)          |  |  |

| 20                                  | 19.2 (63)               | 16.1 (53)        | 13.6 (45)         | 11.4 (37)         |  |  |

| 40                                  | 22.8 (75)               | 19.2 (63)        | 16.1 (53)         | 13.6 (45)         |  |  |

| 100                                 | 28.7 (94)               | 24.2 (79)        | 20.3 (67)         | 17.1 (56)         |  |  |

Table 3.4 shows that for a minimum detectable signal that is 6 dB above the receiver noise floor, a representative aircraft is detectable at 2.8 degrees off of the vertical axis to more than

Figure 3.1 Maximum range versus radar cross section.

Figure 3.2 Half power range versus radar cross section.

1.5 times the required altitude. Minimum detectable signals up to 12 dB above the receiver noise floor surpass the required detection altitudes for all representative aircraft. Note that because the antenna is used to transmit and receive radar signals, a 3 dB reduction in antenna gain yields an overall reduction in the calculation of 6 dB.

#### 3.3 Maximum Time to Intercept Analysis

Having shown that the SRS has sufficient power to detect the representative aircraft at their service ceilings, it now must be shown that this detection can take place in a sufficiently short amount of time to guarantee that the LIDAR is disabled in advance of any intercept of the laser beam. The basic problem is illustrated in Figure 3.3.

Figure 3.3 Calculation for time from detection to intercept, Tint.

The PRF or pulse repetition frequency of the radar is an important parameter for this problem. Of the available PRF's for the Raytheon radar, the 750 Hz setting delivers the

maximum average power. This is the highest frequency setting that delivers the longest available pulse (700 ns). Other settings using higher PRF rates and shorter pulses are available from the radar and are intended for shorter range operation. It should be noted that at the 750 Hz PRF setting, the radar cannot detect targets that are at altitudes under 450 meters due to the radar receiver's response to the radar's transmission of its pulse. This will be explained in more detail in Chapter 5. Targets down to 300 meters are detectable using the 1500 Hz PRF setting which transmits a 250 ns pulse.

It can be seen from Figure 3.3 that the minimum velocity of an aircraft to intercept the laser without being detected is given by the following formula:

$$v_{\min} = y * \tan \theta / T_{\text{int}}$$

(3.3)

The angle  $\theta$  is half of the 3 dB beamwidth of the parabolic antenna or 2.8 degrees. For example, if  $T_{int}$  is taken as ten 750 Hz periods or 13.3 milliseconds, then the minimum velocity necessary to intercept the beam without the aircraft being detected is 7923 km/hr. Table 3.1 gives the maximum level speed of the fastest aircraft considered as 981 km/hr. At this velocity and an altitude of 300 meters, the value for  $T_{int}$  is on the order of 50 milliseconds. Considering this extreme case of an aircraft cruising in excess of 900 km/hr at a 300 meter altitude, the radar would has more than 35 pulses at the 750 Hz PRF with which to detect it. When considering altitudes above 300 meters and/or representative aircraft velocities less than 900 km/hr, an increasing number of radar pulses is available due to the increased value of  $T_{int}$ .

It is necessary to determine then, how many consecutive radar returns from an aircraft will be required to designate a shutdown condition for the laser. This involves a tradeoff between the probability of detection and the probability of false alarm. Every radar receiver has a finite amount of noise associated with it creating a statistical process for the detection of any one radar return. The probability of detection for an individual radar pulse is determined by examining several parameters. By determining the signal to noise ratio of the radar return pulse and choosing a probability of false detection that is acceptable to the application, a probability of detection for a single pulse can be determined [9,10,12].

For example, Figure 3.4 shows that for a 12 dB SNR signal and a probability of false detection of 10<sup>-6</sup>, the probability of detection of a single pulse is 0.7. A cumulative probability of detection may be determined by examining more than one return from the radar target. To achieve the cumulative probability of detection for a target which requires that any one of N radar returns is detected, the following equation is used [11].

$$p_c = 1 - (1 - p_d)^N (3.4)$$

where:

$p_c = probability of cumulative detection,$

$p_d$  = probability of detection of one pulse,

N = number of returns.

It can be seen from Equation 3.4 that as more pulses are reflected from a target, the probability of detection of that target increases. Figure 3.5 shows an example calculation for Equation 3.4 for a cumulative detection probability of 0.99999. With N = 35 and a

Figure 3.4 Required signal-to-noise ratio for single-pulse detection [9].

Figure 3.5 Probability of detection for a single radar pulse versus the number of pulses returned from the target for a cumulative probability of detect of 0.99999.

probability of detection of one pulse of 0.7, any of the representative aircraft will be detected with a probability approaching 1.0. If only 10 pulses are received with a single pulse detection probability of 0.7, the cumulative probability of detection is still 0.999994.

The probability of false detection for the previous example is prohibitively high. To reduce the probability of false detection it is necessary to examine more than one consecutive return pulse. This technique is referred to as pulse integration. Figure 3.6 shows how the probability of false alarm for a given probability of detection is improved by the integration of pulses received by a linear detector. The combined probability of detection of two or three consecutive radar return pulses lowers the probability of detection for the combined event. For example, with a probability of detection of 0.7 for a single pulse, the probability of detecting two consecutive pulses is 0.49 or the product of the probability of detection for each single pulse. Similarly, three consecutive pulses yields a probability of detection of 0.343. For the previous example which considered 10 radar pulses, the cumulative probability of detection for two consecutive pulses is 0.998. When considering a 12 dB SNR signal, a probability of false detection of less than 10<sup>-10</sup> is then achieved. Similarly, considering 10 pulses for three consecutive pulses yields a cumulative probability of detection of 0.965 with a probability of false detection of less than 10<sup>-12</sup>. When considering the large number of pulses available on a target as discussed earlier, the lowered detection probability for each event is of no consequence. The integration of two or three radar return pulses by the Safety Radar subsystem will still yield a detection probability approaching one because the number of pulses available for integration was shown to be at least 35.

Figure 3.6 Required signal-to-noise ratio for detection with noncoherent integration of pulse; linear detector, nonfluctuating signal,  $p_d = 0.75$  [9].

## 3.4 Analysis Summary

The preceding analysis shows that the Safety Radar subsystem, with the Raytheon R72 as its primary component, meets or exceeds necessary parameters to protect aircraft from intercepting the laser in the atmospheric LIDAR system. Maximum range parameters were shown to be met for all representative aircraft. It was shown that the aircraft are detectable well within the necessary time prior to a potential intercept of the laser beam. The probability of detection of a target was shown to approach one for the representative aircraft.

Aircraft flying at altitudes above 300 meters and up to a Boeing 747-400's maximum level cruising speed, are detectable and the laser will be disabled well in advance of any laser beam intercept.

To demonstrate the Safety Radar subsystem as a reliable system, it is necessary to address other effects known to influence the detection of radar signals. Signals transmitted at microwave frequencies are susceptible to absorption by clouds and scattering by rain. At the subsystem's transmit frequency of 9.4 GHz, absorption by clouds accounts for only a loss of on the order of 0.01 dB/km. Scattering by rain at this frequency can account for a more significant loss in signal. Table 3.5 gives characteristic values of loss caused by scattering effects based on the rate of rainfall [11]. It should be noted that at rainfall rates over 25 mm/hr (1 in/hr), the range performance of the subsystem becomes significantly affected.

The Doppler effect is of no consequence for this application due to the 3 MHz bandwidth of the receiver. A radar target would be required to have a velocity relative to the radar greater than 86078 km/hr to shift the received return pulse out of the band of the receiver.

Table 3.5 Scattering loss of 9.4 GHz signal transmitted in rain [11].

| Rate of Rainfall, mm/hr (in/hr) | Scattering Loss, dB/km |  |

|---------------------------------|------------------------|--|

| 1.25 (0.05)                     | 0.02                   |  |

| 5 (0.2)                         | 0.09                   |  |

| 25 (1)                          | 0.9                    |  |

The above analysis places the following requirement on the custom hardware as denoted in Figure 2.3 as the Laser Safety Radar Controller (LSRC). The LSRC must detect shutdown conditions by performing pulse integration of up to three pulses and disabling the laser within 1 millisecond when such a condition is found. This requirement is met by the LSRC as shown in Chapter 4. In addition, self monitoring features were added to the hardware to disable the laser in the event of a detected failure of a subsystem component.

### Chapter 4

### **Custom Hardware Design Description**

#### 4.1 Original Design

In June of 1993, the original version of the Laser Safety Radar Controller (LSRC) was designed and constructed by W. Moyer of the Applied Research Laboratory at the Pennsylvania State University [14,15]. This design monitored two signals from the radar denoted as TRIG and VD. TRIG is the main radar timing signal. It generates its characteristic waveform as shown in Figure 4.1 for each radar pulse that is transmitted. The second signal monitored is VD, which is the detected radar signal utilized by the radar's display to indicate targets. Figure 4.1 shows the relationship for TRIG and the actual transmission of the radar. The parameters listed for the recurrence of TRIG and the pulse width of the radar transmission are obtained using the 750 Hz PRF setting of the R72 radar. The discussion that follows on the original LSRC design is described completely by Moyer [14,15].

The original radar interface circuit is described in a block diagram in Figure 4.2. It was designed as a circuit card mounted in close proximity to the R72 radar unit. The circuit detects transitions of the TRIG signal and the VD signal. The transitions of the TRIG signal are regular as depicted in Figure 4.1. The transitions of the VD signal depend on what targets the radar signal encounters. The signal is normally at zero volts and swings negative to a maximum value of -4 volts when a target is detected. In addition, at approximately 500 ns after the radar begins the transmission of its pulse, a negative pulse appears on the VD signal. This pulse is on the order of 4  $\mu$ s in length. A plot showing the relationship of the pulse on

Figure 4.1 Relationship of radar TRIG signal to actual radar transmission.

Figure 4.2 Block diagram of original laser safety controller circuit.

VD to the TRIG signal is shown in Figure 4.3. This pulse is caused by the transmission of the radar signal and the changeover of the radar's front end hardware from a transmit mode to a receive mode. The switching is necessary to protect the sensitive radar receiver from the high power transmit pulse. A blanking function is implemented in the hardware to allow for the this first transition of the VD signal to be ignored. The amount of blanking selected for the circuit is set up through manual switch settings located on the circuit card.

The circuit monitors the VD signal beyond the selected blanking interval and stores transitions that occur. If a transition that exceeds a fixed negative threshold is found on the VD signal following two consecutive TRIG signals, the laser is disabled. The control of the laser is accomplished through the LSRN signal. This optically coupled, TTL level signal must be in a logic one state (greater than 2.8 volts) for the laser to be enabled. After power up of the circuit or following a shutdown condition, a START/RESET switch must be activated to continue operation of the LSRC and enable the laser if no further shutdown condition is detected.

As noted by Moyer [14], the original circuit is relatively simplistic. This aside, it proved the concepts of interfacing to the radar signals and issuing a disable signal when a target was detected. During field tests, it was found that the target detection method used by the circuit is susceptible to interference from other radar units operating nearby. Although some pulse averaging was accomplished, no target range information is considered in the decision to disable the laser. Two noise pulses on the VD signal that exceed the fixed

Figure 4.3 Relationship of radar VD signal to radar TRIG signal.

negative threshold at different times relative to the TRIG signal will invoke a shutdown of the laser. The circuit also lacked a computer interface for flexible control of the circuit and monitoring of status. It was determined that a revised LSRC was needed to overcome the limitations of the original.

### 4.2 Design Overview

The basic design of the original LSRC is incorporated in the new hardware. Figure 4.4 shows the block diagram of the processing of the detected radar target signals for the current LSRC. The detection methods for the TRIG and VD signals are a direct copy from the original design. These circuits implement high speed voltage comparators and needed no improvements or modifications from the original design. The features added to the original LSRC include a computer interface for setup, control, and status information, built-in testing functions (BIT), dynamic variation of the threshold used to detect the VD signal, implementation of a range bin algorithm for target detection and an on card display for visual reference of the current status.

A separate feature of the LSRC was added to the design to make the Safety Radar subsystem less susceptible to other radar units operating at the similar frequencies and PRF rates in the same locale. This feature is referred to as a pulse staggering or PRF jittering [11]. The block diagram for this function is shown in Figure 4.5.

Figure 4.4 LSRC block diagram - main processing.

Figure 4.5 LSRC stagger controller block diagram.

## 4.3 Functional Description

The LSRC incorporates synchronous circuit design. The main clock is a 16 MHz, TTL level oscillator which drives a clock divider circuit implemented in a programmable logic device (PLD). The following sections describe the details of the major functional blocks of the LSRC. The schematics for the circuits described are located in Appendix A. Also included in the Appendices are a parts list for the circuit card assembly, a hardware/software interconnect diagram, the programmable logic code, written in ABEL, for the PLDs used and source code written in the C programming language used to generate detection threshold data for a programmable read-only memory (PROM).

#### 4.3.1 Radar Pulse Stagger Controller

Modifying the characteristic PRF of the radar in the Safety Radar subsystem causes the timing of the transmitted and received pulses to differ from other radar units operating with similar parameters. This makes the pulses transmitted more easily distinguishable from those transmitted by other radar units. The pulse stagger concept is illustrated in Figure 4.6.

Figure 4.6 Pulse staggering of a radar transmission with alternate long and short intervals between pulses.

In the case shown with no pulse stagger implemented, Radar B appears as a target at a fixed range to Radar A. By delaying every other transmission of Radar A by a fixed amount, the false target shown to Radar A by Radar B changes apparent range enough that it will not be detected as a target by the range bin controller described in Section 4.3.3. By selecting a delay time for every other radar pulse of 2 µs with a 750 Hz PRF, the false target produced by Radar B appears to Radar A to shift by 300 m in 1.33 ms. A real target causing this effect would be traveling at 225000 m/s. With the stagger algorithm, use of a two pulse detection

method should eliminate false target acquisitions due to other radars with operating characteristics similar to the R72.

To implement the stagger controller in the subsystem it is necessary for the LSRC to alter the PRF rate generated by the R72 prior to its transmission. A careful analysis of the schematic for the display unit of the R72 reveals a jumper position that allows for it to be triggered by an external source. In an effort to keep the R72 signals isolated from the LSRC signals, opto-isolators are used to both receive the R72's master PRF clock and output the staggered PRF clock. The electrical interfaces used were suggested by the opto-isolator manufacturer for the device families present on the display unit of the R72.

The radar pulse stagger algorithm is implemented in a PLD. A delay of 0-6  $\mu$ s in 2  $\mu$ s increments is implemented. The delay selection is accomplished through 2 control bits from the computer interface. The input master PRF clock is a 50 percent duty cycle, 750 Hz clock. The PLD implementing the stagger algorithm detects this input with a 500 kHz clock by double buffering and edge detecting it to overcome any possible metastability problems associated with detecting an asynchronous signal. This process induces an additional pseudo-random jitter of the output pulse of up to 2  $\mu$ s. The final output will delay the first of two pulses by 0-2  $\mu$ s and the second of two pulses by 2-8  $\mu$ s as dictated by the selection value. The stagger function may be disabled completely by disconnecting it from the R72.

### 4.3.2 Target Detection Threshold Controller

The original design of the LSRC used a fixed threshold voltage to detect signals on the detected radar target signal VD. To increase the sensitivity of the detection of long range targets, a dynamically varying threshold circuit was implemented.

Figure 4.7 shows a block diagram for the circuit. The VD signal from the radar is nominally zero volts and falls negative to -4 volts when a target is detected. VD is routed through a voltage divider circuit and then into a voltage comparator and is detected if it falls to a threshold value set at the comparator's input. The voltage divider biases the signal to 2.5 volts when VD is zero. The output of the voltage divider drops by half of the negative voltage excursion of VD. As an example, an excursion on the VD signal of -1 volt causes the output of the voltage divider to fall from 2.5 volts to 2 volts. Measurements of the VD signal have shown up to +/-500 mV of noise. To avoid false detection due to noise transients, the maximum threshold value for the comparator considered for detection is 2.1 volts. VD signals falling to within 5 mV of the threshold are detected and a corresponding TTL level pulse is output from the voltage comparator.

A control bit from the computer interface controls whether a fixed or a dynamic threshold is used for VD detection. If a fixed threshold is selected, the controller continuously outputs the first address of the PROM which contains the desired detection level. This level is currently set at 1.9 volts.

If a dynamic threshold value is selected, the controller, after receiving the detected TRIG signal, issues an address to a PROM containing threshold values every 2  $\mu$ s. The

Figure 4.7 Target detection threshold controller block diagram.

controller also issues a latch signal to the D/A converter. This latch signal is output for the first 512 µs after each TRIG. At that point, the value of the threshold remains fixed until the next trigger. Figure 4.8 illustrates the threshold value changes that occur for this algorithm as it is currently programmed. All of the 2048 addresses of the PROM contain a valid threshold value. These values are generated by a program written in C and shown in Appendix E. For this application with 1.33 ms between triggers (750 Hz PRF), only 667 address of the 2048 available in the PROM are accessed. It should be noted that the code for the PROM can easily be modified to adapt to any desired threshold algorithm.

#### 4.3.3 Range Bin Controller

The original LSRC design, because it did not consider the range of a target, was susceptible to the false detection of targets due to noise and other radar signals. The LSRC design incorporates a range bin algorithm in an effort to curtail false detection. Range information can be extracted from a received radar return based upon the delay from the time it was initially transmitted. With a radar signal traveling at or near the speed of light, the range of a target is 150 meters for every 1 microsecond of delay time.

A range bin is a quantization of the range values for detected targets. For example, if a range bin size of 100 meters is chosen, targets found between 0 and 99 meters are placed in the first bin, while those between 100 and 199 meters are placed in the second bin and so on. The quantization level chosen for an application depends upon the range accuracy that is required.

Figure 4.8 Detection threshold values relative to radar pulse transmission.

For this application, a simple range bin algorithm was desired to make the LSRC less susceptible to detection of false targets and still maintain all of the detection capability of the original design. A bin size of 150 meters was selected corresponding to a delay time of 1 µs per bin. Targets are required to be in a given range bin for at least two consecutive radar transmissions to be considered a target. To avoid any detection problems caused by a target directly on a range bin boundary, two overlapping search windows are implemented. The windows overlap in time by 500 ns and the radar return signal is sampled for targets at 125 ns intervals. If a target is found in either search window, the corresponding bin is marked as containing a target. If a target is within 500 ns of the edge of either search range, the bin for both windows is marked as containing a target. A functional timing diagram in Figure 4.9 illustrates the overlapping search ranges and range bins algorithm. It can be seen from Figure 4.9 that if a target falls in the middle of a search range, only one range bin is marked with a target as in the case of targets A and C. Targets B and D fall 500 nanoseconds from the edge of a range bin, causing two range bins to be marked as containing the targets. In this manner all boundary conditions due to range quantization are considered. For a real target to move from one range bin to the next in one transmission of the radar would require it to change its range relative to the radar by 75 meters in 1.33 milliseconds or 202500 kilometers per hour.

The circuit is implemented with a PLD and a 4k x 4 static random access memory (SRAM). A blanking function as described in Section 4.1 is implemented as part of the range bin algorithm. Eight control bits are accepted by the circuit from the computer interface. Each bit carries a weight of 125 ns for a maximum blanking interval of 32 µs.

Figure 4.9 LSRC target search and range bin algorithm.

Radar returns are not detected as targets during the blanking interval. Because time is measured in the LSRC with respect to the initial falling edge of the radar's TRIG signal, the blanking must be set to at least 8 µs to blank out the transmission feedback pulse shown in Figure 4.3 for the radar operating at the 750 Hz PRF rate.

At power up or reset of the circuit, the range bin controller PLD writes logic zeroes to all of the memory locations within the SRAM. These locations are then read back into the controller to ensure that all locations are at logic zero. If any logic one levels are found, the laser enable signal (LSRN) is not issued to the laser. Once the SRAM has been checked, the controller begins detecting targets in the overlapping window fashion described previously. The LSRN signal is not issued to the laser until it has been determined that no targets are present in any range bin for three consecutive radar transmissions. As targets are detected, logic one levels are written to the memory locations in the SRAM that represent the range bins. After each radar transmission, each range bin is read to determine if a target was present there previously. The range bin controller will look for a target in a given range bin for either two or three consecutive radar transmissions before disabling the laser. The number of consecutive passes used to determine a valid target is selected by a control bit issued from the computer interface.

When a valid radar target is found, the laser is disabled and the range bin number is made available to the computer interface. This eight bit number represents the number of microseconds delay encountered from the initial falling edge of the radar's TRIG signal to

the time the target is detected. It may be converted to an estimated target range by the following formula,

$$ETR = 150 * (RBN - 5.5),$$

(4.1)

where:

ETR = estimated target range (meters),

RBN = range bin number.

The -5.5  $\mu$ s in the formula is derived from the fact that the actual radar transmission occurs approximately 6.5  $\mu$ s after the TRIG pulse and that the LSRC requires 1  $\mu$ s to detect it.

#### 4.3.4 Built-in-Test Functions

Several built-in-tests are performed on the LSRC. In the event of a failure of any of these BIT functions, an error condition is generated, causing the laser enable signal to be changed from an asserted to an de-asserted state. Worst case timing analysis shows that the laser enable signal is changed from an asserted to an de-asserted state in less than 2 microseconds for either a detected hardware failure or a detected target.

The time delay between the radar's trigger signals is continuously monitored. If more than 2.56 ms elapses between triggers, an error is flagged and a radar malfunction error is reported via the computer interface. The time allowed before a radar error is reported is 25 percent more than any currently known PRF rate used by the R72 radar. The main purpose of this function is to detect a failure of the radar and it is not intended to flag minor inconsistencies in the radar's PRF rate. A radar error is also generated if the radar is operated

at the 2000 Hz PRF rate. This mode was intended only for short range operation and the 80 ns pulses are not detectable by the LSRC.

One PLD on the LSRC acts as the central built-in-test controller for the monitoring function used to detect device failures. This device periodically issues signals to four other PLD's on the LSRC. The signal is toggled from a logic high to a logic low and back again. If the expected response is not received, an error is flagged and the device causing the error is reported to via the computer interface and the on card display.

Another feature of the LSRC is the on board seven segment display which reflects encoded status messages and is driven by the built-in-test controller. The status of the circuit may be decoded as shown in Table 4.1.

Table 4.1 LSRC encoded display interpretation.

| Displayed Value | Interpretation                                           |

|-----------------|----------------------------------------------------------|

| 0.              | Waiting for first trigger from radar                     |

| 0               | LSRC OK                                                  |

| 1.              | Shutdown for target                                      |

| 2.              | Shutdown for radar malfunction                           |

| 3.              | Shutdown for failure of SRAM test                        |

| Α.              | Shutdown, suspect failure of STD Controller device       |

| b.              | Shutdown, suspect failure of Clock Divider device        |

| c.              | Shutdown, suspect failure of Stagger Controller device   |

| d.              | Shutdown, suspect failure of Range Bin Controller device |

| 8.              | Shutdown, BIT failure - cause unknown                    |

#### 4.3.5 STD Interface Controller

The LSRC is designed with an STD bus interface to allow it to be controlled and monitored via an embedded controller or microprocessor. Control bits are used to reset the

LSRC, set up the amount of desired pulse stagger for the transmitted PRF, turn the dynamic radar detection threshold algorithm on and off, set up the desired amount of blanking and to set the number of consecutive times that a target must be found in a given range bin to classify it as a target. Valid ranges and values for these parameters as well as a description of the available status information is contained in the LSRC Interconnect Diagram shown in Appendix C.

#### Chapter 5

#### Safety Radar Subsystem Test

### 5.1 LSRC Bench Testing

A prototype Laser Safety Radar Controller (LSRC) as described in Chapter 4 was constructed by the author in a wire-wrap configuration. The wire wrap board was first tested in a laboratory environment using simulated radar signal inputs. An STD based computer was not initially available. Set up conditions for the LSRC were accomplished using DIP switches designed into the wire wrap card. Proof of design tests were performed in this manner on all of the LSRC functions. Refer to the schematics in Appendix A for connection points discussed for the individual tests.

#### **5.1.1** Stagger Controller Test Results

A TTL level square wave was input to the stagger control circuit and the waveform received is shown in Figure 5.1 (Figure 5.1 is not drawn to scale). With the input applied to J4-2, the output was monitored at J4-5. Table 5.1 shows the measured delay times for each valid value of the stagger control bits.

Figure 5.1 Measured delay of staggered output.

The 4 +/- 2 microsecond delay of the signal is induced by the detection of an asynchronous signal by a 500 kHz clock and is expected. The table shows that the circuit operates as expected, adding 0, 2, 4 or 6 microseconds of delay to every other pulse.

Table 5.1 Measured delay values of staggered output.

| Value of Stagger Control<br>Bits (MSB to LSB) | Delay Value<br>a (μs) | Delay Value<br>b (μs) |

|-----------------------------------------------|-----------------------|-----------------------|

| 00                                            | 4 +/- 2               | 4 +/- 2               |

| 01                                            | 4 +/- 2               | 6 +/- 2               |

| 10                                            | 4 +/- 2               | 8 +/- 2               |

| 11                                            | 4 +/- 2               | 10 +/- 2              |

## 5.1.2 Target Processing Test Results

To simulate trigger and target inputs, two pulse generators were used with the simulated TRIG input applied to J2-5 used as a trigger for a delayed signal simulating the radar target on VD. Adjusting the amount of delay moved the "target" range as required. In this manner, the blanking, detection threshold variance and the range bin algorithm were verified to operate as expected. Simulated targets were input at the ranges shown in Table 5.2 and the LSRC was shown to pull the LSRN signal low indicating a laser shutdown condition was detected. The value of the target range was determined by reading the value of the register using an oscilloscope. Initially, the threshold algorithm was disabled and a fixed detection voltage of 1.95 volts was used. The commanded blanking value was then set to 12 µs with the simulated target at 10 µs and the LSRN signal remained at its high level as expected. The blanking value was then placed at 9 µs and the target was detected.

Table 5.2 LSRC response to simulated radar targets.

| Simulated Target Range | Reported Target Range | LSRN = Logic Zero |

|------------------------|-----------------------|-------------------|

| (µs)                   | (µs)                  | (Shutdown)        |

| 10                     | 8                     | YES               |

| 40                     | 38                    | YES               |

| 80                     | 78                    | YES               |

| 90                     | 88                    | YES               |

The time constant of the detection circuit for the radar TRIG signal induces a delay of approximately 1  $\mu$ s. This is the main source of the discrepancy between the reported range and simulated range. The range values are intended for reference only and the estimates have an uncertainty of +/- 300 meters.

The above tests were repeated after enabling the thresholding algorithm and the results were re-verified. BIT functions were tested and verified by removing appropriate components to simulate hardware failures.

#### 5.2 Integration of the LSRC with the Raytheon Radar

The next phase of testing of the LSRC required it to interface with the Raytheon R72 radar. A LIDAR research instrument designed at the Pennsylvania State University known as the WAVE-LARS system (LARS) also incorporates a radar safety subsystem using the R72 radar unit and the original version of the LSRC described in Chapter 4. The wire wrap LSRC was installed into this system to finalize the proof-of-design testing. The antenna was placed in an outdoor location pointing at an area with no air traffic for the following initial tests.

### 5.2.1 Verification of Blanking and Range Bin Functions

The time between the falling edge of the radar's TRIG signal and the end of the transition of the radar's target detection indicator VD caused by the transmission of the radar was measured and verified to be 9  $\mu$ s when operating the radar at a 750 Hz PRF with a 700 ns transmission pulse. Refer to Figure 4.3. With the blanking value commanded to be less than 9  $\mu$ s, the status display for the LSRC showed it to be in a shutdown state due to a target. Note that the LSRN signal was tested to ensure that is was in the de-asserted state when the shutdown status was reported. This same condition was tested for both available range bin algorithms and was found to operate as expected. The blanking value was then set to 9.5  $\mu$ s and it was verified that no shutdown conditions occurred.

#### 5.2.2 Verification of Pulse Stagger Function

The pulse stagger function was enabled and the tests described in Section 5.2.1 were executed to verify that altering the transmissions of the radar did not affect operation. All four settings for this function were tested in this manner and the subsystem operated as expected.

#### 5.2.3 Verification of Target Detection Threshold Function

The target detection threshold function was enabled and the tests described in Section 5.2.1 were again executed to verify that the operation of the subsystem was not affected.

## 5.3 SRS Testing Summary

Tests conducted by the author on the Safety Radar subsystem involved pointing the radar antenna at fixed targets and monitoring the status display on the LSRC to determine the state of the hardware. Trees and mountains at ranges from less than one kilometer and up to 11 kilometers caused the subsystem to immediately enter a laser shutdown state. Estimated range values read from the LSRC correlated with the range to target values shown on the radar display. A final set of tests were conducted which involved pointing the radar antenna at moving aircraft. Approximately ten trials were run on small to medium aircraft whose distances from the radar ranged from 4 to 10 kilometers. The Safety Radar subsystem was shown to enter its shutdown state in all trials run.

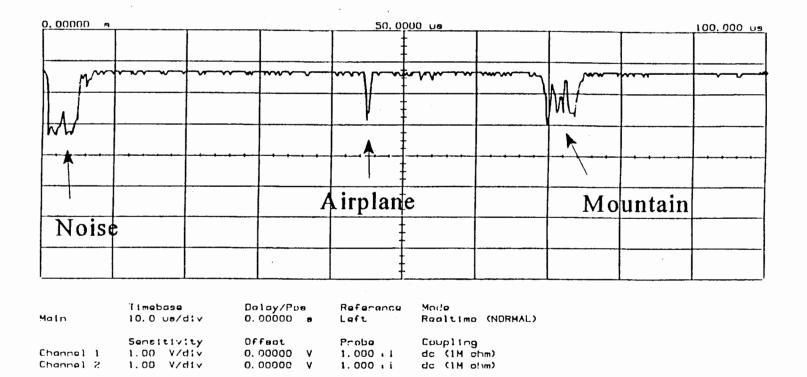

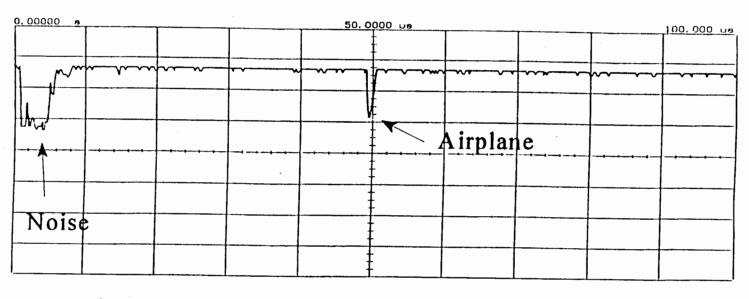

The Raytheon R72 radar has been extensively tested for its use in this application. Data taken by Jim Yurak using the R72 in the LARS safety subsystem is shown in Figures 5.2, 5.3 and 5.4. These figures show the response of the radar's VD signal when detecting aircraft in three separate trials [13]. In addition, field testing of the subsystem with the original LSRC was accomplished at the Point Mugu Naval Air Station in Point Mugu, California. During these tests, a Navy A-7 Corsair II aircraft performed 46 fly-bys at

different altitudes and orientations. The subsystem successfully detected the aircraft and invoked a shutdown of the laser for each trial [13,16].

A printed circuit version of the LSRC is currently in the process of integration into the LAPS system by the Applied Research Laboratory (ARL). The documentation given in the Appendix reflects the design as it exists to this point. Baselines for the wire wrap and printed circuit designs are currently being maintained by ARL.

Further field testing of the Safety Radar subsystem with the LSRC hardware is necessary to prove its safety and reliability. Tests to verify the maximum and minimum ranges of the subsystem should be executed with the hardware in both two pulse and three pulse integration modes. The subsystem should be tested at both the 1500 Hz and 750 Hz PRF rates to determine the optimal operating condition. Finally, the subsystem should be operated in areas where other marine radars are transmitting with its pulse staggering engaged to verify proper operation.

Figure 5.2 Time plot of R72 radar detection of aircraft at 5.3 km range [13].

Figure 5.3 Time plot of R72 radar detection of aircraft at 6.8 km range [13].

| Moin                   | Timebase                                | Delay/Pos                        | Reference                     | Mode                                   |

|------------------------|-----------------------------------------|----------------------------------|-------------------------------|----------------------------------------|

|                        | 10.0 us/div                             | 0.00000 s                        | Left                          | Raaltime (NOSMAL)                      |

| Channel 1<br>Channel 2 | Sensitivity<br>1.00 V/div<br>1.00 V/div | Offeet<br>0.00000 V<br>0.00000 V | Probe<br>1.000 .:<br>1.000 :: | Coupling<br>dc (IM ohm)<br>dc (IM ohm) |

Figure 5.4 Time plot of R72 radar detection of aircraft at 7.4 km range [13].

### Chapter 6

#### Conclusions

#### 6.1 Summary of Features

The Safety Radar subsystem offers a valid solution to the problem of protecting operating aircraft from the hazard presented by the use of an atmospheric LIDAR system. Through the use of a commercially available marine X-band radar, the subsystem is cost effective, reliable and easily maintained. The addition of a parabolic dish antenna in place of the delivered sweep antenna yields a 5.6 degree protection zone around the laser. The radar provides more than adequate coverage for this area up to the maximum flight ceilings for commercial aircraft. The LSRC hardware interfaced to the radar provides several key features for the subsystem. Several self monitoring functions are provided for the hardware and radar to ensure safe failure modes in the event of a detectable error or malfunction. Functions added to increase the reliability of the subsystem include the implementation of range gating and pulse staggering. Each of these features should reduce false shutdown conditions caused by noise and the operation of other X-band radars. The computer interface allows for a flexible subsystem that can easily be adapted to changing operational requirements without modifying the hardware.

Caution is advised in the following areas: 1) applications of a Safety Radar subsystem as described in this thesis that bypass or inhibit any of its safety features must be carefully analyzed to insure that all possible failure modes of the modified system have been considered; 2) no components should be added between the Safety Radar subsystem and the laser Q-switch inhibit without careful re-evaluation of all safety issues and extensive analysis.

# 6.2 Operational Considerations

It is recommended for maximum safety that the Safety Radar subsystem be operated only in areas where air traffic is encountered in level flight or in shallow angles of ascent or descent to ensure a maximum radar cross-section is available to the radar. These aircraft should also be operating at altitudes above 300 meters.

Operation in rain or snow conditions at precipitation rates of more than 25 mm/hr (1 in/hr) is expected to degrade the maximum detection range performance.

The Safety Radar subsystem contains a computer interface such that it can be easily controlled via an embedded controller or microprocessor on the STD bus. The status of the radar and the LSRC hardware is continuously available to the computer. The hardware, once it enters a shutdown state will not re-enable the laser until such time as a reset is commanded by the computer. The computer program is thus expected to handle these shutdown conditions and determine when it is appropriate to reset the subsystem and resume searching for targets. After a reset, the hardware will not enable the laser until three radar transmissions have occurred with no targets detected.

The LSRC hardware is aware of the TRIG pulse sent to it from the radar but has no way of determining if the transmission of the radar pulse actually occurred. One possible solution to this is to construct a radar band power detector that would interface directly to the computer. This device would contain an RF power detector, a passive component that outputs a DC level based upon the RF power level it receives. With a small dipole antenna mounted in the vicinity of the parabolic dish antenna and a feed running to the detector, only simple signal conditioning

techniques would be required to interface it to the computer and determine that radar transmissions were occurring.

For the subsystem to determine the status of the radar receiver, the blanking value should periodically be set back to the point that the radar transmission feedback pulse is in the detection range and verify that it is received as a target.

Calibration of the radar's transmitted power and receiver sensitivity using a radar test set is recommended at approximately six month intervals along with a visual inspection of both the radar and the custom hardware.

Before the Safety Radar subsystem can be used as a completely autonomous instrument, further field testing is required with the use of human observers. Proven performance in this mode of operation will yield the confidence necessary to move toward the goal of an unattended subsystem.

### 6.3 Suggestions for Future Work

Further design work to enhance the capabilities of the Safety Radar subsystem could be investigated in the following areas: (1) the external detection of the radar transmissions discussed earlier in this chapter; (2) development of software to automatically set up the blanking value for a selected PRF rate; (3) development of a separate instrument to detect targets under 300 meters; (4) design enhancements to the LSRC including using a RAM in place of the EPROM in the variable detection threshold circuit.

#### References

- [1] Schmeisser, E. T., Laser exposure effects on visual functions: measurements by electrophysiology a selective review, *Laser Safety, Eyesafe Laser Systems, and Laser Eye Protection*, SPIE Vol. 1207, pp.14-15, January 1990.

- [2] Winburn, D. C., Practical Laser Safety, Marcel Dekker, Inc., pp. 19-25, 1990.

- [3] Philbrick, C. R., et al., LAMP TO LAPS: The Transition from a Research to an Operational LIDAR Sensor for Atmospheric Properties, Vol V, LAMP LIDAR SAFETY PLAN, 30 September 1992.

- [4] Philbrick, C. R., et al., Measurements of the High Latitude Middle Atmosphere Dynamic Structure Using Lidar, Environmental Research Papers, No. 967, Hanscom AFB, Massachusetts, 18 February, 1987.

- [5] Model R70 Series Raster Scan Radar Systems, Instruction Manual, Raytheon Marine Company, Hudson, New Hampshire.

- [6] Interoffice Correspondence, Electrical Test Report, AS15-90 15 inch Diameter Antenna, Seavey Engineering Associates, Inc., Cohasset, Massachusetts.

- [7] 1990-1991 Jane's Aircraft, Marston and company, ltd.

- [8] Skolnik, Merrill I., *Introduction to Radar Systems*, McGraw-Hill Book Company, New York, New York, 1980.

- [9] Blake, Lamont V., *Radar Range-Performance Analysis*, Lexington Books, Boston, Massachusetts, 1980.

- [10] Knott, Eugene F., Shaeffer, John F., Tuley, Michael T., *Radar Cross Section*, Artech House, Norwood, Massachusetts, 1993.

- [11] Stimson, George W., *Introduction to Airborne Radar*, Hughes Aircraft Company, El Segundo, California, 1983.

- [12] Wiley, Richard G., *Electronic Intelligence: The Analysis of Radar Signals*, Artech House, Norwood, Massachusetts, 1982.